静态时序分析STA

目录

概念

设计都会有性能指标,为了保证在物理制造后的电路功能正确并且满足设计指标,需要保证电路的时序满足设计要求,这就需要在电路设计好后对电路进行时序分析,满足时序才能进行接下来的设计和制造。

- 动态时序仿真

动态时序仿真是针对给定的输入信号波形,模拟电路实际工作时候的功能和延迟情况,给出相应的仿真输出波形。它主要用于验证设计在器件实际延时情况下的逻辑功能。由动态时序仿真报告无法得到设计的各项时序性能指标,如最高时钟频率等.(但是到底怎么来做不会)

既能验证设计的功能,也能验证设计的时序。

- 静态时序分析

静态时序分析是分析每条路径上器件和连线延迟信息,计算出设计的各项性能,比如最高时钟频率,建立保持时间等。

只能验证设计的时序信息,不能验证设计的功能。

STA优缺点

- 从动态时序仿真转到静态时序分析

在初期集成电路设计中,动态时许仿真来验证设计的时序很流行。但是随着设计规模不断增大,进行动态时序仿真需要花费大量时间设计时序向量和功能向量(用来验真功能和时序的),并且还不一定能保证100%覆盖率。所以快捷的静态时序分析受到青睐。 - STA优点

- 分析速度块

- 不需要仿真向量

3)覆盖率几乎100% - 静态分析还能完成动态仿真不能完成的复杂分析。例如最大最小路径延迟、建立保持时间分析、时钟信号质量分析。

- STA缺点

- 不能验证设计的功能

2)STA只能分析同步时序电路,对于异步电路,只能在门级动态仿真来验证

3)不能自动识别特殊路径。比如多周期路径(multi-cycle path),非正常路径(fault paths),多时钟周期关系(multiple clocks)(这些到底是什么现在还不清楚txtx)

所以STA并不能完全取代动态时序仿真,二者必须协同存在

- 不能验证设计的功能

STA的作用

- 确定芯片的最高工作频率

通过时序分析可以控制工程的综合、映射、布局布线等环节,减少延迟,从而尽可能提高工作频率 - 检查时序是否满足

可以通过时序分析来查看目标模块是否满足约束,如不满足,可以定位到不满足约束的部分,并给出具体原因,进一步修改程序直至满足时序要求 - 分析时钟质量

时钟存在抖动、偏移、占空比失真等不可避免的缺陷。通过时序分析可以验证其对目标模块的影响

STA的过程

- 将设计打散成一个个timing paths

- 计算每一条path上的延迟

- 检验延迟是否满足设计要求

时序分析基本概念

- 建立时间(setup time)

- 保持时间(hold time)

- 恢复时间(recovery time)

置位或复位信号在时钟信号有效之前需要保持有效的最小时间,类似于setup time - 移除时间(removal time)

置位或复位信号在时钟有效沿之后需要继续有效的时间。

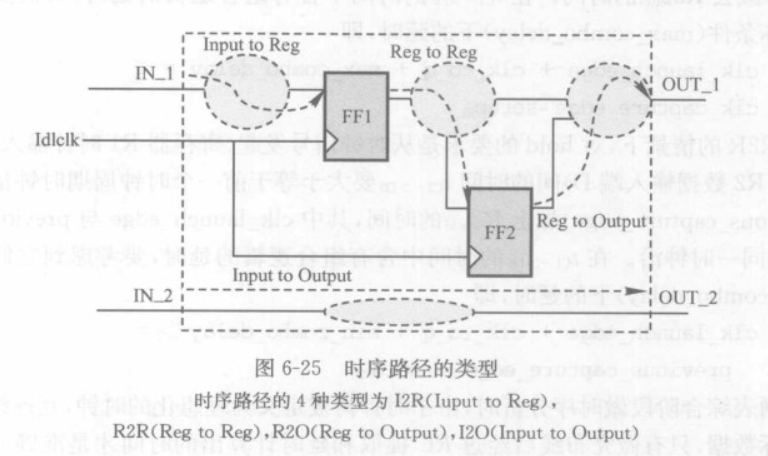

时序路径

- 触发器到触发器

- 输入端口到触发器

- 触发器到输出端口

- 输入端口到输出端口

静态时序分析的基本方法

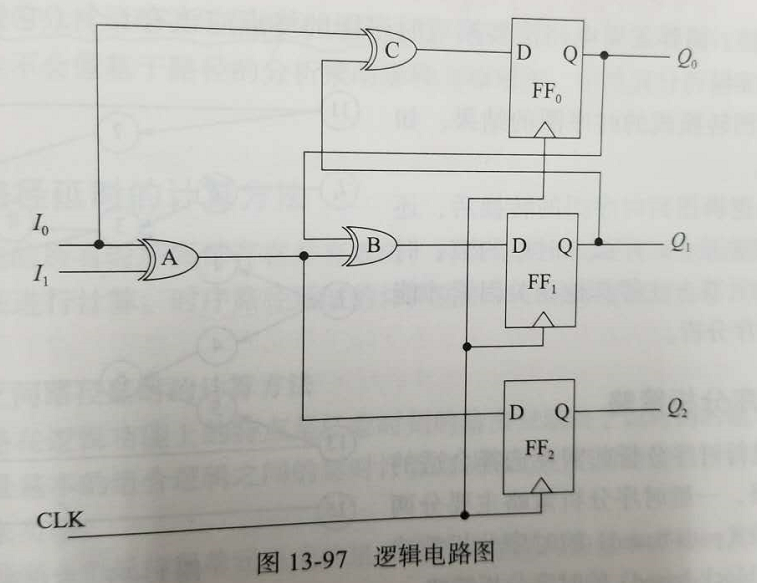

下图是一个逻辑电路图

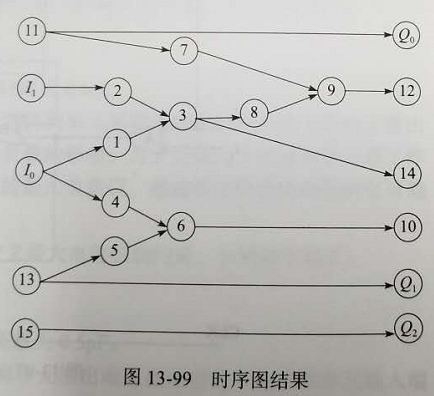

设定好逻辑节点,可以得到时序图中间结果

确定好时序图的输入和输出,得到最终的时序图

时序图的起点:输入端口、时序单元的输出和存储器输出

时序图的中点:输出端口、时序单元的输入和存储器输入

本博客所有文章除特别声明外,均采用 CC BY-SA 4.0 协议 ,转载请注明出处!