vcs使用

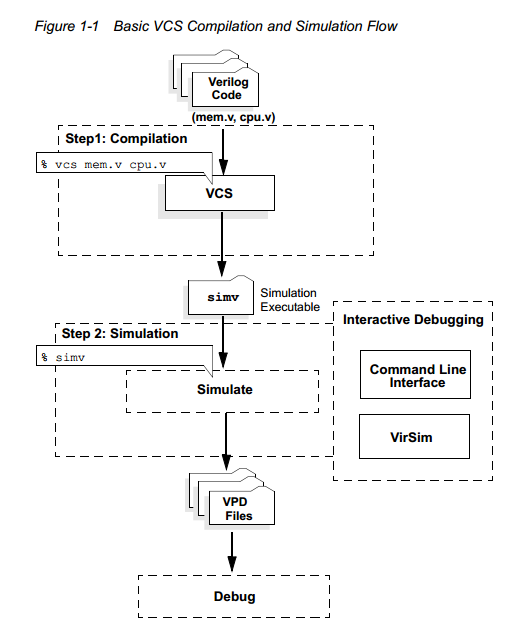

VCS仿真流程

VCS将.v文件(verilog模型)编译成可执行二进制文件(simv),然后运行可执行文件进行仿真。

常用options

- **-l filename **

将需要编译的文件的地址写在filename文件下,每行一个文件

-R

编译之后直接运行simv进行仿真-sverilog

识别system Verilog语法

- -full64

在64bit环境下编译和仿真

- +v2k

IEEE 1364 -2001年的Verilog语法

- +notimingcheck

Disables timing check system tasks in your design. Using this option at runtime can improve the simulation performance of your design, depending on the number of timing checks that this option disables.

- -debug_all

交互仿真,不知道具体什么意思,不过一般都是加这个的,这样可以用$finish来控制仿真停止。

- +incdir + 目录

在目录下搜索哪些`include指定的文件

9) -y 目录

在目录下的文件中搜索module的定义。

10) +libext+.v+.sv

配合-y使用,搜索目录下指定后缀的文件

11)+define+macro

定义宏,+define+ASSERT_ON

12) +lint=TFIPC-L

如果有的模块的端口定义了,但是没有连接,用这个选项,编译器会给出哪些端口没有连接

13)+vcs+vcdpluson

生成vpd波形文件

仿真时加上自定义的选项 $value$plusargs

功能:通过添加仿真选项,在仿真的时候控制代码的执行。

语法:

integer = $value$plusargs(“plusarg_format”,signalname);

The plusarg_format argument specifies a user-defined runtime option for passing a value to the specified signal. It specifies the text of the option and the radix of the value that you pass to the signal.

比如存在代码:

1 | |

仿真脚本:

simv +r1=10

monitor的输出:

g:

r1=x at 0

r1=0 at 1

r1=10 at 2

上面的r1变量是用户自己指定的,仿真的时候代码会读取到这个值,读取成功返回真,失败返回假。也可以用这个传进来的值来控制代码执行,比如作为if语句的判断条件。

本博客所有文章除特别声明外,均采用 CC BY-SA 4.0 协议 ,转载请注明出处!