通过RISC存储程序机理解数据通路控制器设计

RISC存储程序机

RISC存储程序机SPM,该电路的程序和数据存储在存储器中。该电路有三个部分控制器、处理器(数据通路)和存储器。通过流水线设计(用寄存器打断)实现同时的指令获取、译码和执行。

结构框图如下:

1.处理器

处理器部分包括寄存器(包括四个通用寄存器,Program Counter,Instruction Register、地址寄存器add_R等)、ALU、复用器、数据通路等。

上图中标出了数据流动的路线,寄存器赋值、复用器选择受到外部控制信号作用。

2.ALU

ALU中的运算指令:

ADD 求和,

SUB 减法,

AND 按位与,

NOT取反

3.控制器

上图(figure 7-10)中左边是controller,RISC机的所有操作都受控制器控制,控制器根据当前的指令将各个控制信号给到处理器和memory。

控制器的设计依赖于ALU的性能、数据通路资源和可用时钟方案。

| 控制信号 | 操作 |

|---|---|

| Load_Add_flag | 加载地址寄存器 |

| Load_PC | 将Bus_2上的内容写到PC |

| Load_IR | 加载指令寄存器IR |

| Inc_PC | PC加一 |

| Sel_Bus_1_Mux | 选择Mux_1的驱动源 |

| Sel_Bus_2_Mux | 选择Mux_2的驱动源 |

| Load_R0 | 加载R0 |

| Load_R1 | 加载R1 |

| Load_R2 | 加载R2 |

| Load_R3 | 加载R3 |

| Load_Reg_Y | 将Bus_2的内容写到Reg_Y |

| Load_Reg_Z | 将ALU的输出写入Reg_X |

| Write | 将Bus_1的内容写入memory |

4.指令集

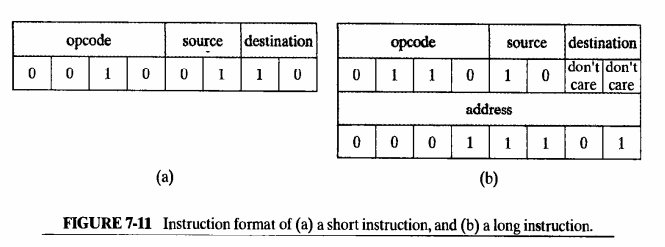

RISC机根据存储器中的指令序列进行操作,那么就必须预先定义好指令集内容。本次中的指令有一个字节的也有两个字节的,如下图所示

对于单字节指令,前四位是指令的操作吗,后四位是源寄存器地址和目的寄存器地址。

对于双字节指令,前四位是指令的操作码,后四位是源寄存器地址或目的寄存器地址,由指令类型决定;第二个字节给了操作数在存储器中的地址。

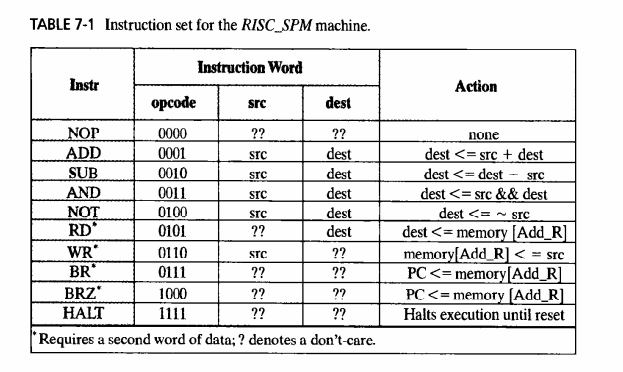

所有指令如下:

单字节指令

NOP:不执行任何操作,寄存器保持原值,源目的地址无效

ADD:源和目的寄存器中的内容相加,将结果保存到目的寄存器

SUB:源和目的寄存器中的内容相减,将结果保存到目的寄存器

AND:源和目的寄存器中的内容按位与,将结果保存到目的寄存器

NOT:源寄存器内容取反,保存到目的寄存器

双字节指令

RD:从第二个字节(地址)指定的存储单元位置取出数据存到目的寄存器,忽略源寄存器

WR:将源寄存器的数据取出存到第二个自己指定的存储单元位置,忽略目的寄存器

BR:从第二个字节指定的存储单元的内容存入PC,实现分支跳转,忽略源和目的寄存器

BRZ:当零标志位有效的时候,从第二个字节指定的存储单元的内容存入PC,实现分支跳转,忽略源和目的寄存器

下面给出每条指令的编码:

5.控制器设计

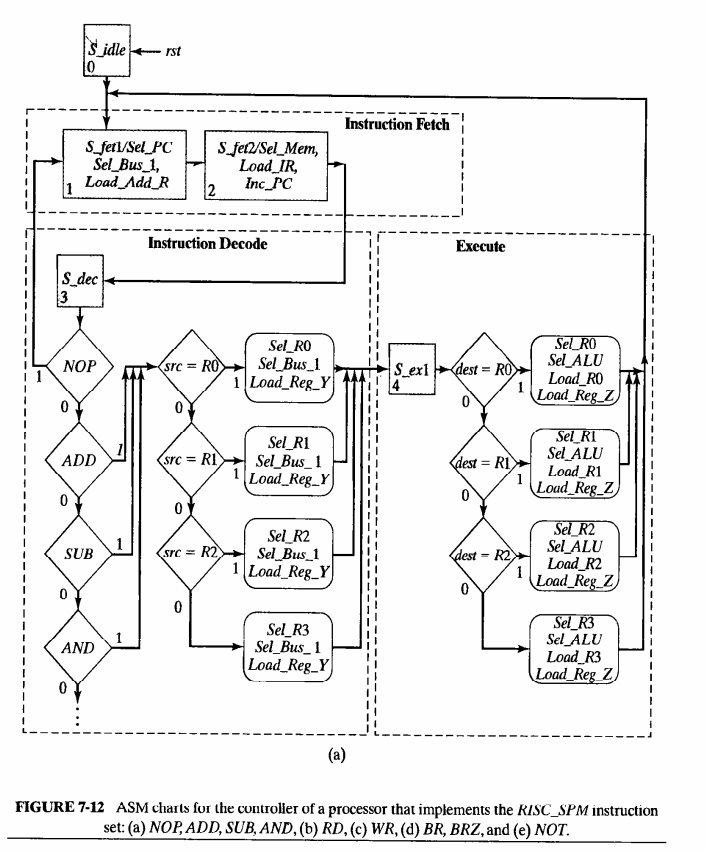

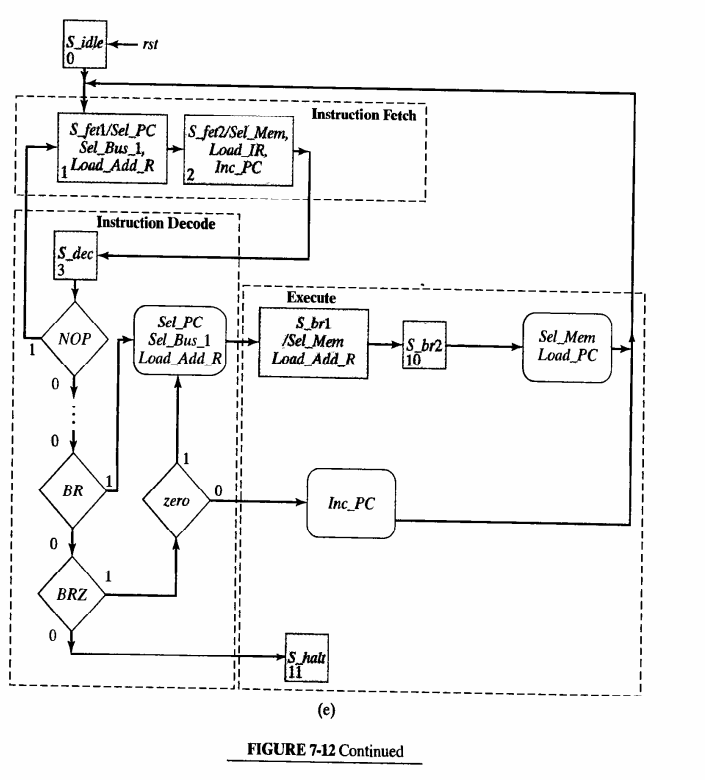

根据指令定义状态机的状态,根据译码结果实现状态的跳转。

该RISC机指令的执行分成三个阶段,取指、译码和执行。取指阶段分成两个周期,第一个周期加载地址寄存器Add_R,第二个周期从存储器中将指定地址处的内容取出给到指令寄存器IR。译码阶段一个周期完成。执行阶段根据不同指令类型分为0、1、2个周期,其中NOT指令可在译码周期内完成,单字节指令如ADD在一个周期内完成计算并将结果写入目的寄存器,其中源寄存器在译码阶段加载。双字节指令,如RD,需要两个周期,第一个周期将指令的第二个字节载入地址寄存器,另一个周期从指定的存储器单元位置读取数据写到目的寄存器。

根据上面分析,可以分成如下11个状态,需要两个周期的阶段有两个状态。

各个状态

| 各状态名 | 描述 |

|---|---|

| S_idle | 复位后进入该状态,不执行任何操作 |

| S_fet1 | 将PC值加载到地址寄存器Add_R,(复位操作会将PC值初始化位其实地址),复位无效后的第一个有效时钟进入该状态;NOP指令译码结束也进入该状态 |

| S_fet2 | 将地址寄存器指定地址中的内容载入到指令寄存器,并将PC值加一 |

| S_dec | 对IR的内容译码,产生一些数据通路和寄存器的控制信号,控制状态的跳转。如果是双字节指令,需要加载地址寄存器 |

| S_ex | 单字节指令执行ALU操作,设置零标志位,将结果存入目的寄存器 |

| S_rd1 | 将RD指令第二个字节从memory中加载到地址寄存器,PC+1 |

| S_rd2 | 将S_rd1状态指定的存储器位置取出数据存入目的寄存器 |

| S_wr1 | 将WR指令第二个字节从memory中加载到地址寄存器,PC+1 |

| S_wr2 | 将源寄存器的内容村早S_wr1状态指定的存储器单元位置 |

| S_br1 | 将BR指令第二个字节从memory中加载到地址寄存器,PC+1 |

| S_br2 | 将S_br1指定的存储器单元地址存到PC |

| S_halt | 发生指令异常,进入默认状态 |

下面几幅图给出根据译码结果执行不同指令的ASM图

一下几张图要参考代码来看,书中附带的代码

单字节指令的ALU运算

RD指令

WR指令

NOT指令

BZ BRZ指令

6.处理器

根据下面这张图中处理器里面的模块例化出来,端口连接好就行,具体见代码

本博客所有文章除特别声明外,均采用 CC BY-SA 4.0 协议 ,转载请注明出处!