跨时钟域设计

1. 同步、异步定义

对于工具来说,只要给出了时钟之间的关系,工具就认为是同步时钟,tool就可以对这两个时钟分析时序关系。

同步时钟:能够明确定义以下属性的时钟:

- 时钟周期或者频率

- 时钟占空比 duty time

- 每个时钟信号第一个上升沿的时间(相位)

- 时钟的输入latency——从PLL到模块的时钟输入端口的delay

异步时钟:没法明确定义上面这些属性的时钟。

比如clk0的周期、占空比、相位、latency都明确定义了,clk1只定义了时钟频率,那么就可以将这两个时钟看成异步时钟。

2. 亚稳态 metastable

亚稳态这东西各种数字书、时序书、文章等都会提到,都有专门的论文将这个metastable,比如Criticality-dependency-aware timing characterization and analysis。

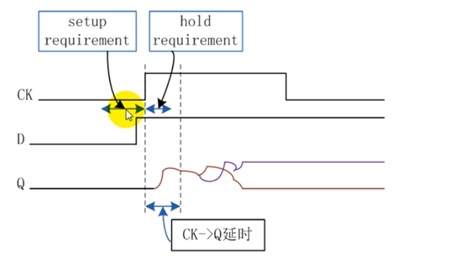

建立保持时间

建立时间:数据在时钟有效沿之前需要保持稳定的时间。

保持时间:数据在时钟有效沿之后需要保持稳定的时间。

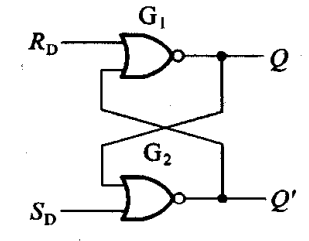

建立时间和保持时间产生的由来是:边沿触发的触发器由锁存器组成的,锁存器是两个与非门或者或非门反馈形成的,反馈回路上有延迟,这样就导致触发器需要建立时间和保持时间,保证触发器建立稳定的反馈,否则就是不稳定,也就是亚稳态喽。

比如下面这张图:

上方(a)图:横轴Tcp-d是时钟有效之前data需要稳定的时间,在上图中也就是从data input到达D开始至clock edge到达CP的时间;纵轴Tcp-q寄存器传播延迟——clock edge(CP)到data output(Q)时间。可见随着Tcp-d增大,Tcp-q区域稳定值,当此时的Tcp-q恶化10%时对应的Tcp-d就是Tsetup时间。如果Tcp-d继续减小,寄存器延迟迅速增长。

灰影区域metastable region亚稳态区域。但是就算是setup slack 小于建立时间,处在亚稳态区域,芯片也不一定失败,因为设计中的路径可能时序裕量较大。但是工艺厂商不保证器件时序正确。保持时间类似,如下图:

亚稳态的两个问题

当建立、保持时间不满足时寄存器处于亚稳态,这回带来两个问题:

- 实际电路中大大延迟了Tck-q的时间,这个Tck-q的值不在工艺库里,需要问foundry到底是多少

- 最终Q端的值不确定,可能是0也可能是1.

3. 跨时钟域处理的目标

为了保证跨时钟域数据(事件)的完整性或正确性:

- 数据(事件)的值不能错

- 数据(事件)的顺序不能错

- 数据(事件)的个数不能错

通过这三点来检验跨时钟域数据传输的正确性。

3. single bit跨时钟域

两级同步跨时钟信号(打两拍)

通常的跨时钟域传递数据会产生亚稳态,采样的异步时钟不知道被采样的data是否已经稳定,或者被采样的data不一定满足采样时钟的建立、保持时间。

一般会采用如下图的打两拍——用两个寄存器将数据稳定一下;并且设置两个用来同步的触发器间Q到D的max delay(set_maximal_delay)。下面会分析为什么要这样。

上图中,clk0,clk1是异步时钟,clk0控制绿色的寄存器,clk1控制两个蓝色的寄存器,我们称两个蓝色的寄存器位同步寄存器。第一个同步寄存器很可能是亚稳态采样,第二个寄存器基本不会亚稳态。

对于第一个同步的寄存器而言是跨时钟域采样,很可能亚稳态,这样第一个寄存器的Tck-q就会很长(这要问foundry,库中器件最大的Tck-q到底是多少,而不是根据库中的信息),比如1ns。

如果同步时钟clk1不是很大,比如不到100Mhz,那么周期T是10Ns,那么对于第二个寄存器来说有足够的setup \hold time来保证不是亚稳态采样。

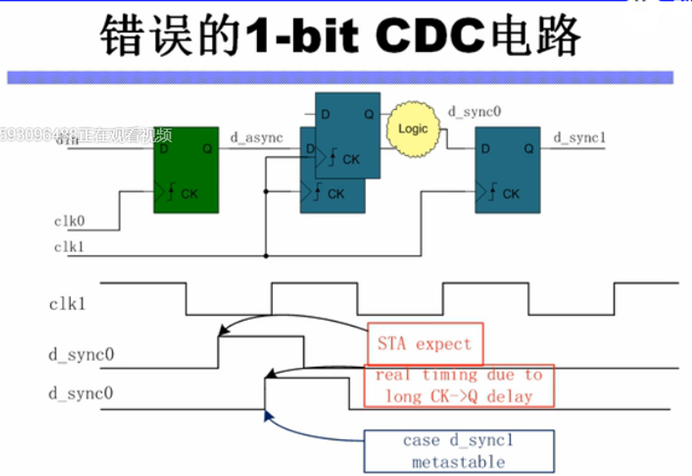

当然如果clk1频率很高的话,由于第一个寄存器亚稳态采样,Tck-q很大,实际中第一个寄存器Q端的输出会向后延迟,使第二个寄存器的setup time不满足。如下图中

上图中由于clk1采样d_async时不满足建立时间,使得第一个同步寄存器亚稳态,其输出端d_async0经过很长时间才稳定,也就是Tck-q时间大大增长,这使得第二个同步寄存器在采样d_async0的时候也发生建立时间不满足,也使得输出端d_async1亚稳态,这样就错了。

这就需要设置第一个同步寄存器Q端到第二个同步寄存器D端的最大延迟(max delay),使这段路径满足建立保持时间约束(T > Tck-q + Tq-d + Tsu)。如下图所示:

跨时钟域可能延迟一个周期

在跨时钟域传输中可能会延迟一个周期,如下图所示

如上图中case0中d_sync0第一个周期采样到了高电平,而case1中d_sync0第一个周期没采样到高电平,其信号延迟了一个周期,这种延迟一个周期是不确定的,但知识一个周期,不会是两个.

错误的single bit采样电路

第一种

上图中组合逻辑电路可能竞争冒险,使同步的寄存器采样到错误的数据

第二种

第一级同步寄存器是会产生亚稳态,那么它的Tck-q就会很大,比如1ns吧,但工具不知道,以为它是正常的满足setup 、hold 的,所以根据库中的Tck-q,比如0.2ns,这样实际中的Tck-q多了0.8ns,所以实际中的d_sync0信号会比工具认为的推迟0.8ns,如第二个d_asyn0信号,这样就有可能使第二级同步寄存器不满足setup time,产生亚稳态。这其实就是上面讨论的。

解决方法就是对Q到D之间的路径加一个MAX DELAY约束,考虑到Tck-q增大的情况。

4. multi bit跨时钟域

对于多位数据跨时钟域传递,如下图:

这样不对,第一级的几个同步寄存器亚稳态时可能会产生四个输出(两位数据,四种情况),产生的数据不是传输的0或者3,这不行

采用握手信号

下图是基于握手信号的多位同步。传递一个数据需要握手4次,传递效率低,但对时钟频率没有特别的要求。

对数据使能信号进行寄存,控制数据采样

下图中,vld控制data信号,当vld有效的时候clk0对data采样。

在异步时钟域中,通过同步寄存器对vld进行寄存,然后用异或门产生一个cap信号,用来控制时钟clk1对data数据采样。

注意:这里没有对data信号寄存,而是对vld信号寄存的

这种方法效率高一些。但要保证vld的脉冲宽度足够宽,至少是clk1的两三倍。

5. 异步fifo

当然异步FIFO时最有效的,异步fifo设计见另一篇文章

当然异步fifo有好多时序上的问题,一般不要自己搞:

- 使用synopsys DesignWare(DW)中的async_fifo IP

- 使用公司里经过TP验证的fifo,当然这要注意一下异步fifo实现的频率,可能100MHZ下可以用1GHZ或者500MHZ下就不行了

- 在FPGA中就用ISE/VIVADO中自带的IP。

6. 后仿中的时序约束

1 . 后仿的时候要设置不让工具检查跨时钟域的setup、hold time,因为肯定会产生亚稳态。

2 . 上面也提到的设置Q到D的最大延迟

7. 在Verilog高级数字设计第五章还有一块介绍异步传输的,

分成两种情况:异步数据脉冲宽度和同步时钟长短

本博客所有文章除特别声明外,均采用 CC BY-SA 4.0 协议 ,转载请注明出处!