UVMPrimer中的DUT改写成Verilog

内容:

讲UVMPrimer书给的代码中的DUT改写成了Verilog形式,原来时VHDL形式,用VCS仿真的时候总是出错,花了大半天改写了。

DUT介绍

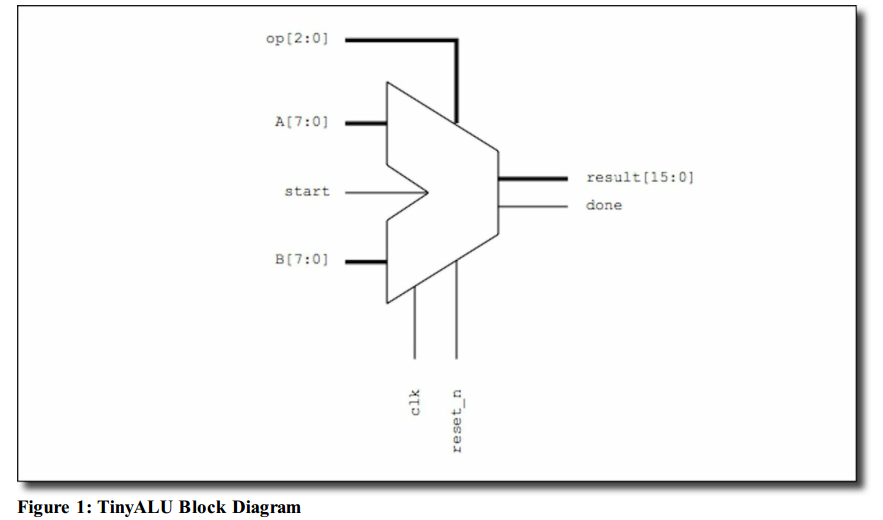

这本书中的DUT是个ALU,模块管脚如下图,

A,B是两个八位的输入,start是启动信号,op是命令信号,包括加,乘,与等,result是计算结果,done是DUT的应答信号,当dut计算结束,done为1。ALU中的计算有单周期,也有多周期的乘法指令。

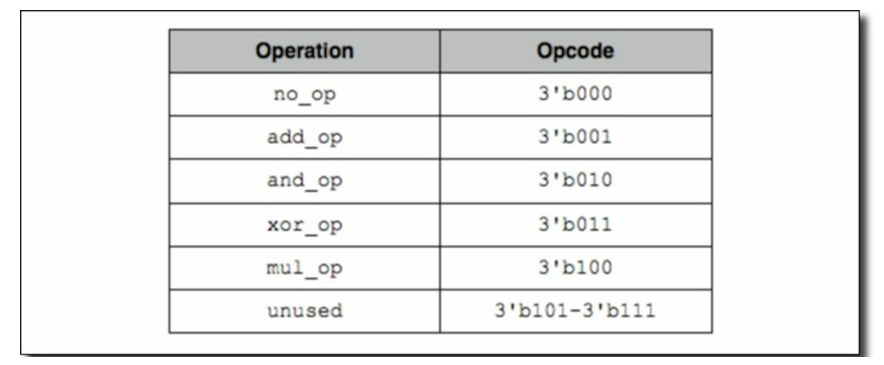

op命令的编码如下:

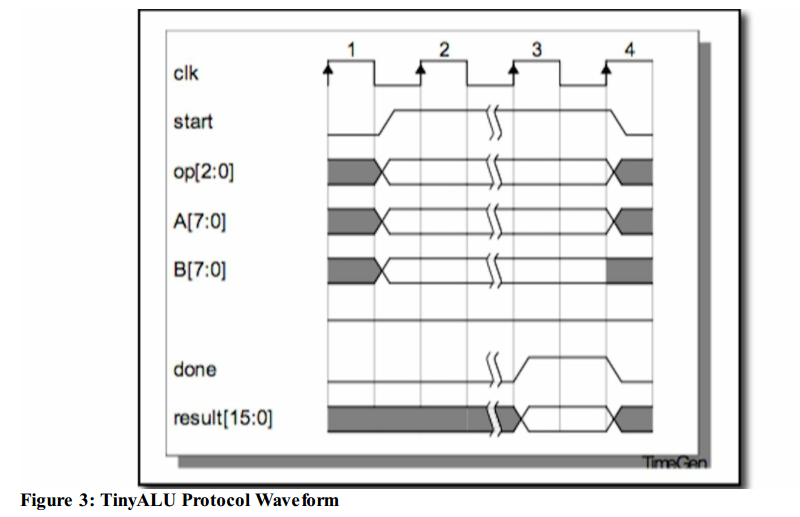

ALU的时序图如下,这就是管脚的协议,设计工程师根据协议来design,验证师根据协议来验证设计是否满足协议。

start有效时,ALU读取op,A,B信号,ALU计算中start一直是高,当ALU计算结束,ALU拉高done信号,此时start可以拉低了,done为高只持续一个周期。

ALU代码:

单周期的指令

1 | |

多周期乘法指令

1 | |

顶层模块

1 | |

所有文件获取

把DUT和验证环境放在了GitHub上,地址

原来

错误:

编码时候出现了一些错误。

定向思维错误。

在连续写多个always过程语句时候,把相似的敏感列表写成了一样的了。这种错误常常发生,就是脑子木了,惯性的敲代码,没过脑子。

给信号result增加寄存器形式result_r,result_r用在过程语句中。result_r的宽度跟result不一致,经常忘了定义宽度。

修改了信号,但是没有改全。

在tb上例化DUT时,连线信号变了,但是例化DUT部分没有改变这个信号。

本博客所有文章除特别声明外,均采用 CC BY-SA 4.0 协议 ,转载请注明出处!