0. 参考

Simulation and Synthesis Techniques for Asynchronous FIFO Design with Asynchronous Pointer Comparisons – Clifford E. Cummings ,Sunburst Design

1. 异步FIFO

异步FIFO是指读数据在一个clock demain,写数据在另一个clock demain的FIFO buffer。

相关参考之前一篇文章 Cummings——异步FIFO第一讲

2. 判断FIFO空满的第二种方法

通常情况下FIFO的空满是通过增加一位地址位来判断的,比如 Cummings——异步FIFO第一讲

中的方法,本文要介绍另一种方法,可以减少寄存器使用。

2.1 满判断

根据地址的高两位将FIFO的地址空间分成四部分,如下图figure2所示:

地址是格雷码地址。如果写地址落后读地址一个地址空间,比如写地址在00空间,读地址在01空间,那么说明写地址快要追上读地址,FIFO快要满了,这时候给一个”possibly going full”位,此时figure4中的direction latch会被set(低电平set,所以figure2中取反了)。

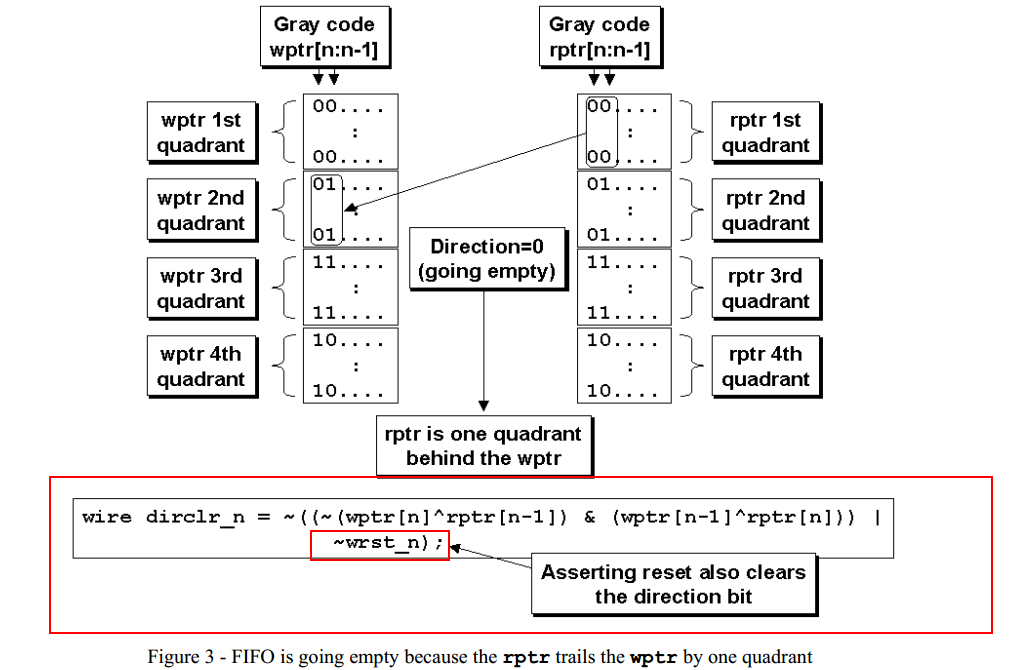

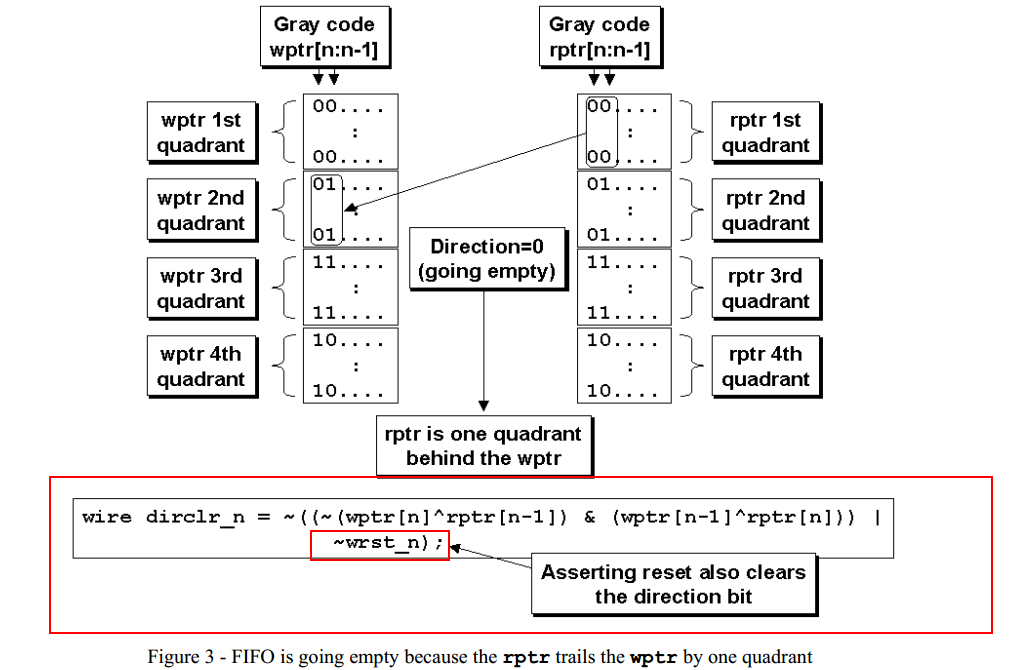

2.2 空判断

空判断与满判断类似,有一个“possibly going empty”位,低电平时将direction latch clear了。如下图,只是这时候

2.3 direction latch

direction为1表示快要满了,如果接下来读写地址相同,则满;为0表示快要空了,如果接下来读写地址相同,则空。

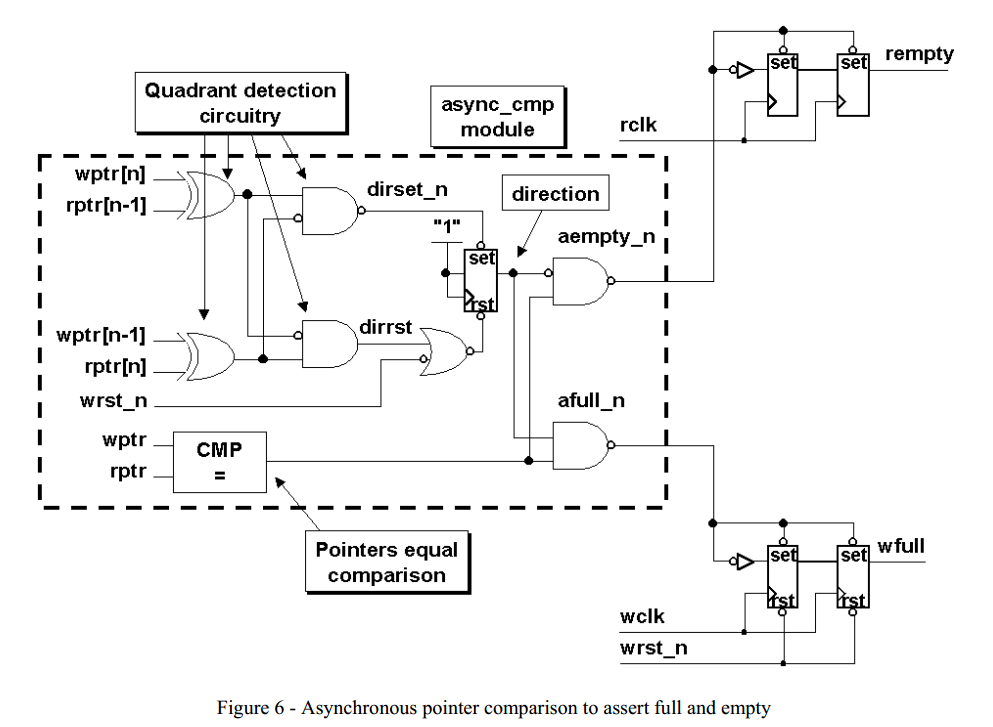

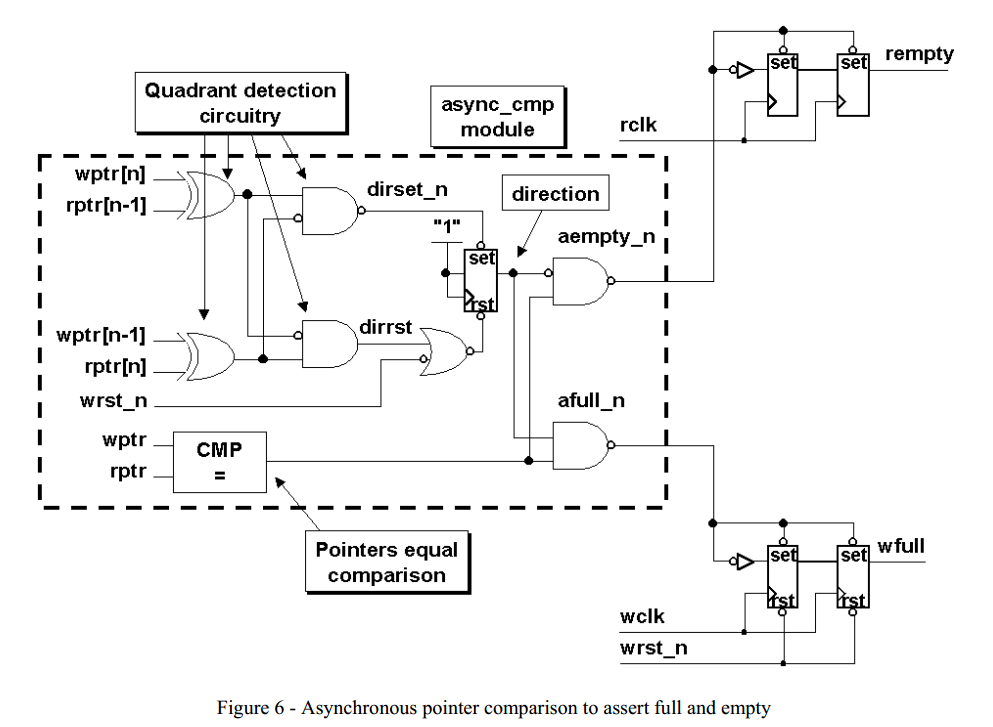

3. fifo结构图

FIFO的结构图如下,空满标志位是在CMP比较逻辑中产生的,在CMP中先生成direction方向位,然后判断读写地址。

4. RTL代码

4.1 top层

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

| module fifo2 (rdata, wfull, rempty, wdata,

winc, wclk, wrst_n, rinc, rclk, rrst_n);

parameter DSIZE = 8;

parameter ASIZE = 4;

output [DSIZE-1:0] rdata;

output wfull;

output rempty;

input [DSIZE-1:0] wdata;

input winc, wclk, wrst_n;

input rinc, rclk, rrst_n;

wire [ASIZE-1:0] wptr, rptr;

wire [ASIZE-1:0] waddr, raddr;

async_cmp #(ASIZE) async_cmp

(.aempty_n(aempty_n), .afull_n(afull_n),

.wptr(wptr), .rptr(rptr), .wrst_n(wrst_n));

fifomem #(DSIZE, ASIZE) fifomem

(.rdata(rdata), .wdata(wdata),

.waddr(wptr), .raddr(rptr),

.wclken(winc), .wclk(wclk));

rptr_empty #(ASIZE) rptr_empty

(.rempty(rempty), .rptr(rptr),

.aempty_n(aempty_n), .rinc(rinc),

.rclk(rclk), .rrst_n(rrst_n));

wptr_full #(ASIZE) wptr_full

(.wfull(wfull), .wptr(wptr),

.afull_n(afull_n), .winc(winc),

.wclk(wclk), .wrst_n(wrst_n));

endmodule

|

4.2 mem读写

mem读写跟第一种FIFO一样, Cummings——异步FIFO第一讲

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

| module fifomem (rdata, wdata, waddr, raddr, wclken, wclk);

parameter DATASIZE = 8;

parameter ADDRSIZE = 4;

parameter DEPTH = 1<<ADDRSIZE;

output [DATASIZE-1:0] rdata;

input [DATASIZE-1:0] wdata;

input [ADDRSIZE-1:0] waddr, raddr;

input wclken, wclk;

`ifdef VENDORRAM

VENDOR_RAM MEM (.dout(rdata), .din(wdata),

.waddr(waddr), .raddr(raddr),

.wclken(wclken), .clk(wclk));

`else

reg [DATASIZE-1:0] MEM [0:DEPTH-1];

assign rdata = MEM[raddr];

always @(posedge wclk)

if (wclken) MEM[waddr] <= wdata;

`endif

endmodule

|

4.3 CMP比较逻辑

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

| module async_cmp (aempty_n, afull_n, wptr, rptr, wrst_n);

parameter ADDRSIZE = 4;

parameter N = ADDRSIZE-1;

output aempty_n, afull_n;

input [N:0] wptr, rptr;

input wrst_n;

reg direction;

wire high = 1'b1;

wire dirset_n = ~( (wptr[N]^rptr[N-1]) & ~(wptr[N-1]^rptr[N]));

wire dirclr_n = ~((~(wptr[N]^rptr[N-1]) & (wptr[N-1]^rptr[N])) |

~wrst_n);

always @(posedge high or negedge dirset_n or negedge dirclr_n)

if (!dirclr_n) direction <= 1'b0;

else if (!dirset_n) direction <= 1'b1;

else direction <= high;

assign aempty_n = ~((wptr == rptr) && !direction);

assign afull_n = ~((wptr == rptr) && direction);

endmodule

|

CMP的框图如下:

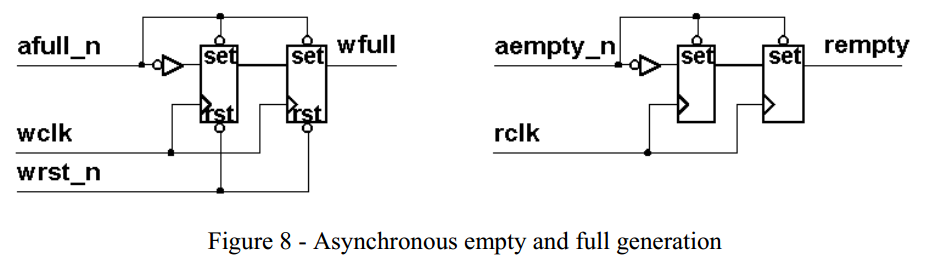

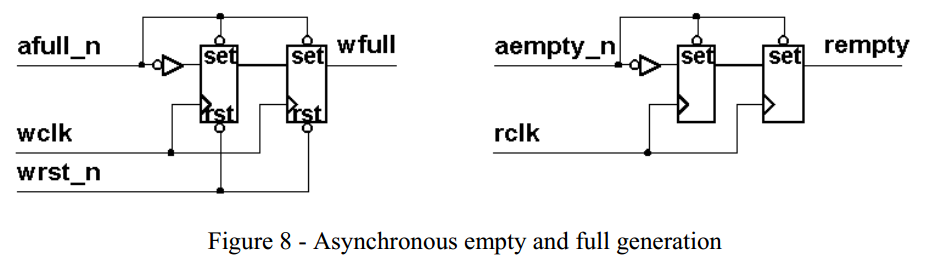

4.3.1 异步的空满产生

aempty_n为0时,empty置位为1.aempty_n为0(也就是空)是在rclk时钟域产生的(因为读数据时候才可能空),而aempty_n为1(也就是空被clear)是在我才离开时钟域产生(因为写数据才不为空)。

同样afull_n是在wclk产生满置位,在rclk满清零。

异步的空满操作:

如果afull_n=0说明满了,满这个状态相比于不满状态持续时间肯定短,如果刚刚满了,但是又接着读数据,那么这个满状态持续时间很短(在rclk的上升沿afull_n=1,使状态编程不满。),如果用wclk对afull_n采样这个满状态0可能不满足建立保持时间,所以就直接将afull_n接到置位上,避免时序不满足。

还可以看出wfull的set不受wclk的影响,这是因为满是由wclk控制的waddr来控制的;wfull的clear需要用wclk用两个周期来同步,这是因为不满是由rclk控制的raddr来控制的,需要用wclk同步一下。

4.3.2 reset操作

如figure6所示,这里的复位信号是wrst_n。如果wrst_n复位,则:

1) 满标志位立马清零。

2) 使读写地址都为零,所以地址比较器输出1

3) direction置为零

4) direction清零值得aempty_n为零,使empty为1.

4.3.3 写与满

置位之后,如果winc有效,则地址比较器输出0,aempty_n为1,两个rclk之后,empty为0.

如果winc继续有效,当waddr落后raddr一个地址空间时,direction为1,表明将要满了。

如果winc继续有效,当waddr等于raddr时,afull_n为0,立马时wfull为1.

4.3.4 读与空

上面写满了,如果接下来要读,即rinc有效,读写地址不同了,afull_n为1,两个wclk之后,full无效。

如果inc接着有效,当raddr落后waddr一个地址空间时,,,后面不必详述了,差不多东西。

4.4 空标志

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

| module rptr_empty (rempty, rptr, aempty_n, rinc, rclk, rrst_n);

parameter ADDRSIZE = 4;

output rempty;

output [ADDRSIZE-1:0] rptr;

input aempty_n;

input rinc, rclk, rrst_n;

reg [ADDRSIZE-1:0] rptr, rbin;

reg rempty, rempty2;

wire [ADDRSIZE-1:0] rgnext, rbnext;

always @(posedge rclk or negedge rrst_n)

if (!rrst_n) begin

rbin <= 0;

rptr <= 0;

end

else begin

rbin <= rbnext;

rptr <= rgnext;

end

assign rbnext = !rempty ? rbin + rinc : rbin;

assign rgnext = (rbnext>>1) ^ rbnext;

always @(posedge rclk or negedge aempty_n)

if (!aempty_n) {rempty,rempty2} <= 2'b11;

else {rempty,rempty2} <= {rempty2,~aempty_n};

endmodule

|

4.5 满标志

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

| module wptr_full (wfull, wptr, afull_n, winc, wclk, wrst_n);

parameter ADDRSIZE = 4;

output wfull;

output [ADDRSIZE-1:0] wptr;

input afull_n;

input winc, wclk, wrst_n;

reg [ADDRSIZE-1:0] wptr, wbin;

reg wfull, wfull2;

wire [ADDRSIZE-1:0] wgnext, wbnext;

always @(posedge wclk or negedge wrst_n)

if (!wrst_n) begin

wbin <= 0;

wptr <= 0;

end

else begin

wbin <= wbnext;

wptr <= wgnext;

end

assign wbnext = !wfull ? wbin + winc : wbin;

assign wgnext = (wbnext>>1) ^ wbnext;

always @(posedge wclk or negedge wrst_n or negedge afull_n)

if (!wrst_n ) {wfull,wfull2} <= 2'b00;

else if (!afull_n) {wfull,wfull2} <= 2'b11;

else {wfull,wfull2} <= {wfull2,~afull_n};

endmodule

|